Google, HP, Oracle Join RISC-V To Make Open Source Processor Core

Short Bytes: RISC, which was only available on commercial platforms in the forms of ARM and MIPS, will soon be open source. Big tech giants including Google, Oracle, HP have agreed to it and its open source version is set to roll out this year in form of RISC-V.

Short Bytes: RISC, which was only available on commercial platforms in the forms of ARM and MIPS, will soon be open source. Big tech giants including Google, Oracle, HP have agreed to it and its open source version is set to roll out this year in form of RISC-V.

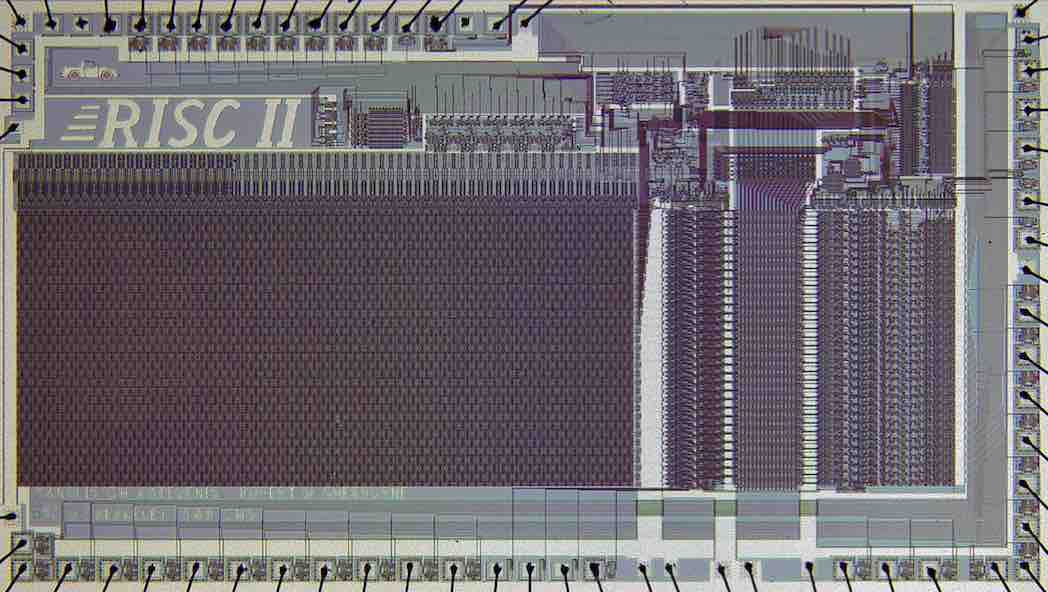

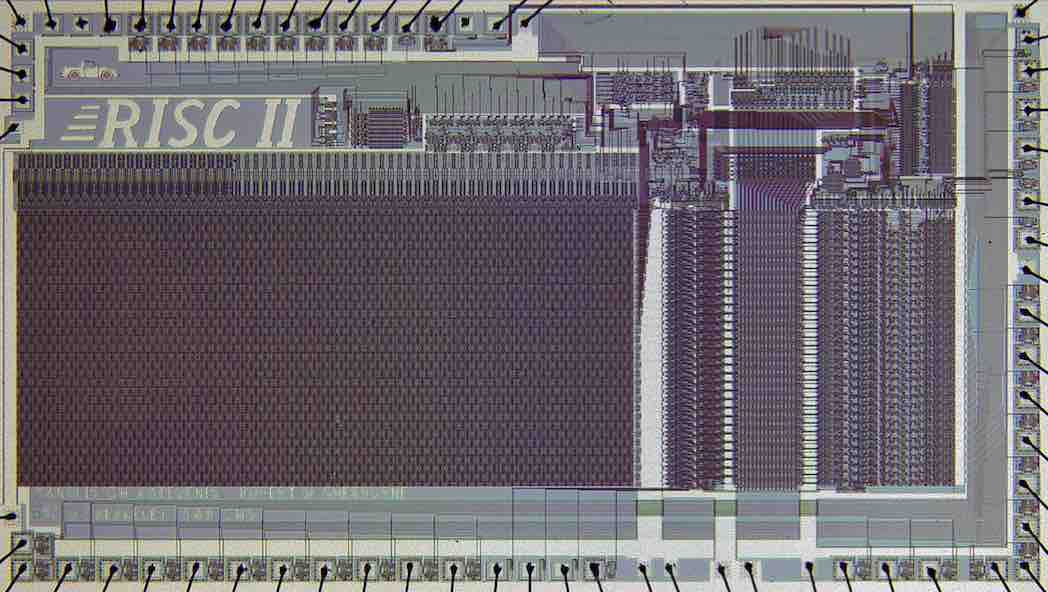

RISC, reduced instruction set computer, is a microprocessor that is designed to perform a small set of computer instructions. MIPS, millions of instructions per second, is the higher version of RISC where the higher number of instructions can be executed per second. However, only commercial versions of RISC are available today in forms of ARM and Mips.

To make it open source, in August 2014, Patterson and colleagues launched an open source effort around the core which will enable a new class of processors and SoCs for small teams that can’t afford licensed cores or get the attention of their vendors. Fifteen sponsors, including a handful of high-tech giants, have agreed to be the first members of its new trade group. Some of the big tech giants are Google, Hewlett-Packard Enterprise (HPE), Lattice, Microsemi, and Oracle — which will be hosting next week’s workshop — will be among the first members of RISC-V.

Also read: This New ‘Skyscraper’ Chip Could Make Computers Run 1,000 Times Faster

This group of tech giants is in the process of drafting the details of the open source license which will be part of its member agreement. The terms will specify a zero-royalty RAND license as well as verification suites licensees must run to use the RISC-V logo. Users will need to contribute as open source any changes they make to the core.

Currently, RISC-V instruction sets run on Linux and NetBSD. Soon this will be available on Android, Windows or any major embedded RTOSes.

Support for other operating systems is expected to arrive in 2016.

Also read: Mozilla Is Betting On Its Open Source IoT Computer Chirimen And It Makes Perfect Sense